Микросхемы серии К1814

Много кричат, что СССР все воровал... на самом деле - копировать практически невозможно. Можно разрабатывать на основе... но так поступает весь мир!

Однокристальные 4-разрядные микроЭВМ серии К1814

Основной тенденцией развития систем управления является переход от полностью централизованных систем к децентрализованным, проникновению автономных управляющих устройств на все более низкие уровни управления. Автоматизация управления на нижних уровнях повышает надежность и живучесть систем, облегчает решение задач комплексной автоматизации. Известно, что расходы на решение задачи будут минимальными, если использовать ЭВМ, наименьшую по производительности из удовлетворяющих заданным условиям. Максимальная простота и дешевизна автоматической системы управления достигаются при использовании однокристальных микроЭВМ, реализующих функции ввода, хранения, обработки, вывода данных и управления на одной БИС.

Интегральные микросхемы серии К1814 представляют собой однокристальные 4-разрядные микро-ЭВМ, предназначенные для построения микроконтроллерных систем управления.

В серию входят:

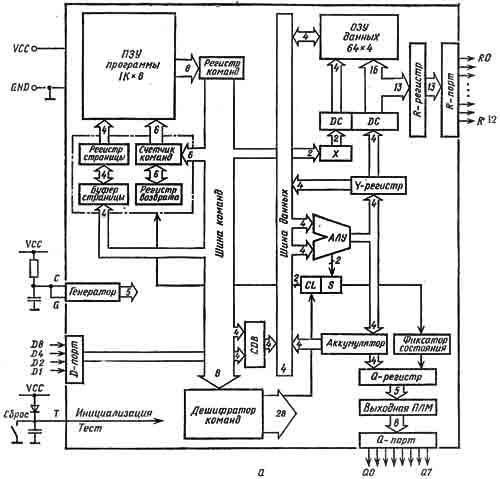

- однокристальная микроЭВМ (ОМЭВМ), которая содержит 4-разрядный процессор, ПЗУ программ емкостью 1К 8-разрядных команд, ОЗУ данных емкостью 64 4-разрядных слов, схемы ввода-вывода и встроенный тактовый генератор;

- универсальная микроЭВМ (УМЭВМ), идентичная по архитектуре однокристальной и отличающаяся тем, что адресует внешнее ЗУ программ и управляет внешней выходной ПЛМ.

ОМЭВМ выполняют функции специализированных микроконтроллеров в соответствии с программой, хранящейся в масочно-программируемом ПЗУ и могут быть применены в периферийных устройствах вычислительной техники, различной контрольно-измерительной, медицинской и бытовой аппаратуре. УМЭВМ предназначена для отладки программ в составе отладочных устройств и для самостоятельного применения в изделиях, производимых в малом количестве, когда разработка однокристального варианта экономически нецелесообразна.

Структурная схема ОМЭВМ и отличительные особенности УМЭВМ приведены на рис. 1. Архитектура микроЭВМ с разделением шины команд и шины данных обусловливает аппаратное и программное разделение адресации программной памяти и ОЗУ данных.

Структура адресации

Адресное поле размером 1К разбито на 16 страниц по 64 байта. Адрес страницы задается 4-разрядным регистром адреса страницы (РА), а 6-разрядный счетчик команд (PC) адресует 64 команды каждой страницы. Счет осуществляется по определенному закону, приведенному в табл. 1. Порядок выборки команд программы изменяется командами условного перехода BR, вызова подпрограммы CALL и возврата из подпрограммы RETN. По командам BR и CALL в PC записывается 6-разрядный адрес перехода из адресного поля (W) этих команд. Одновременно в РА загружается 4-разрядный адрес страницы перехода из буферного регистра адреса страницы (РВ). Для реализации длинных ветвлений в РВ перед командами BR или CALL загружают адрес страницы перехода из поля команды LDP. Если содержимое РА и РВ одинаково, то происходит короткое ветвление программы (переход на той же странице), если в РА из РВ загружается содержимое новой страницы, то происходит длинное ветвление программы с переходом на другую страницу памяти. По команде CALL в регистре возврата из подпрограммы (SR) запоминается адрес возврата в основную программу, а в РВ запоминается адрес страницы основной программы. По команде RETN происходит возврат в исходную программу, содержимое РВ пересылается в РА, а содержимое SR в PC. Команды BR и CALL условны по состоянию триггера состояния S и выполняются, если S = l. В противном случае ветвления не происходит, и в следующем цикле PC адресует последующую команду программы. Такая структура адресации памяти программ проста в программировании, но не позволяет осуществлять вложение подпрограмм и длинные ветвления в подпрограмме.

Структура адресации ОЗУ данных также страничная. ОЗУ емкостью 64х4 бит разбито на четыре страницы по 16 4-разрядных слов. Адрес страницы задается 2 разрядным Х-регистром, адрес слова внутри каждой страницы задается Y-регистром. В отличие от Х-регистра, Y-регистр участвует в операциях АЛУ и является регистром общего назначения (РОМ). Изменение содержимого Х-регистра осуществляется по командам Загрузить Х-регистр (LDX) и Образовать дополнение содержимого Х-регистра (СОМХ).

Арифметическо-логическое устройство

4-разрядное АЛУ выполняет операции сложения, вычитания, арифметического и логического сравнения над операндами, поступающими с шины данных через входные мультиплексоры. Результат арифметической операции через выходной селектор в соответствии с микрокомандами отсылается в один из РОН, аккумулятор или Y-регистр. Одновременно с арифметическими операциями АЛУ производит сравнение входных величин и выработку признака равенства или неравенства операндов. Результат сравнения NE или содержимое разряда переноса CR соответствующими микрокомандами может пересылаться в триггер состояния Входными операндами АЛУ могут быть выходные коды Y-регистра, ОЗУ, мультиплексора данных CDB, прямой или инверсный код аккумулятора и константа 15.

Мультиплексор данных CDB представляет собой логическую схему, предназначенную для выбора и передачи на шину данных входной информации с D-порта, константы С с шины команд или битовой маски для маскирования разрядов при выполнении операций над битами. Пересылки данных в РОН осуществляются через АЛУ путем сложения их с нулем.

Система команд и устройство управления

Базовая система команд (табл. 2) содержит 43 команды. Все команды однобайтовые и имеют один из четырех форматов (рис. 2). Декодирование кодов команд и формирование сигналов управления осуществляются дешифратором команд. На выходе дешифратора формируется горизонтальный микрокод, разряды которого инициируют выполнение микроопераций. Часть дешифратора выполнена на основе ПЛМ мощностью в 30 произведений, причем матрица И осуществляет непосредственное декодирование кода команды, а матрица ИЛИ выполняет функции памяти микропрограмм. Управляющие сигналы, возбуждаемые на выходе ПЛМ, инициируют выполнение комбинаций из 16 программируемых микроопераций. Для обеспечения возможности формирования сложных команд типа чтение-операция-запись выбрана многофазная организация выполнения микроопераций, обычная для горизонтального микропрограммирования. Некоторые операции, связанные с адресацией, вводом и модификацией разрядов, реализуются одной микрооперацией, причем эти микрооперации не используются в совокупности с другими микрооперациями в одном командном цикле. Поэтому с целью экономии микропрограммной ПЛМ формирование сигналов управления для данных операций осуществляется непосредственно на выходе дешифратора (матрица И).

Слово состояния программы

Слово состояния определяется содержанием триггера признака подпрограммы CL и триггера состояния S. Триггер признака подпрограммы устанавливается командой CALL и определяет занесение адреса возврата в стек и блокировку данных переходов в режиме вызова. Таким образом, длина подпрограммы не должна превышать 64 команды. Сброс триггера происходит при возвращении в основную программу по команде RETN.

Триггер состояния определяет разрешение передач управления. Содержимое триггера определяется командой, выполненной в предыдущем цикле. В зависимости от команды триггер состояния принимает безусловное значение «1», значение разряда переноса сумматора или результата сравнения операндов в компараторе. Содержимое триггера состояния через выходной фиксатор состояния SL может быть выведено в выходной регистр Q. Значение фиксатора состояния изменяется только по команде YNEA.

Структура ввода-вывода

МикроЭВМ имеет раздельные схемы ввода и вывода, позволяющие параллельно вводить входные данные и выводить содержимое двух выходных регистров, Q и R на раздельные порты вывода.

Входные данные вводятся в схему через 4-разрядиый входной D-порт и далее через мультиплексор данных поступают на шину данных. Входная информация с D-порта может пересылаться в аккумулятор по команде TDA или в АЛУ для проверки на нуль по команде DNEZ. Выходной регистр Q используется для параллельного вывода данных. Запись в Q-регистр производится по команде вывода TIQ, при этом содержимое аккумулятора и фиксатор состояния SL пересылаются в регистр Q.

Для удобного представления выходной информации Q-порта, например на 7-сегментном индикаторе или другом устройстве отображения информации, в схеме имеется выходной шифратор информации, выполненный на базе ПЛМ мощностью 20 произведений. Матрица ИЛИ ПЛМ имеет восемь выходных линий в соответствии с разрядностью Q-порта. Программирование выходной ПЛМ производится маской в соответствии с требованиями пользователя. В УМЭВМ выходная ПЛМ кодируется как повторитель.

Выходной регистр R имеет 13 индивидуально программируемых ячеек памяти. В одном командном цикле может быть установлена командой SETR или сброшена командой RSTR только одна ячейка R-регистра, адресуемая текущим содержимым Y-регистра. Все ячейки регистра R имеют параллельный выход па выводы R-порта. Индивидуальное программирование выходных линий R-порта позволяет эффективно использовать их для непосредственного управления исполнительными устройствами, стробирования входных и выходных данных, сканирования клавиатуры, дисплея и других применений.

Машинный цикл

Разделение шин команд и данных позволяет организовать двухуровневый конвейер операций, совместить циклы выборки и исполнения команд. При такой организации время выполнения операций определяется длительностью машинного цикла микроЭВМ, а не полного цикла команды. Длительность машинного цикла составляет шесть тактов генератора, или 20 мкс на частоте 300 кГц, и одинакова для всех команд, что очень удобно при программировании задач в реальном масштабе времени. Синхронизация схемы в пределах цикла осуществляется пятью фазами, часть которых приведена на рис. 3. Здесь же указаны временные интервалы выполнения различных микроопераций, для команд вывода приведены временные диаграммы.

Начальная установка и сброс микроЭВМ

Начальная установка микросхемы в исходное состояние: РА = РВ = 15, PC = 0, Q = 0, R=0, CL = 0 — осуществляется при включении питания с помощью специальной схемы. Поддержка внутренней схемы инициализации при работе с источниками питания, не обеспечивающими крутой фронт нарастания напряжения в микросхеме, происходит по выводу Т путем создания задержки установки уровня нуля на данном выводе внешней емкостью. Разряд емкости при отключении питания выполняется диодом. Сброс микроЭВМ в начальное состояние производится путем установки на выводе Т высокого уровня на время не менее шести машинных циклов при нулевой информации на входах D-порта. Состояние схемы после сброса аналогично состоянию после начальной установки.

Синхронизация

МикроЭВМ может работать в режимах с внешней и внутренней синхронизацией. В первом случае тактовые импульсы подаются на вход С с внешнего генератора, во втором — при подключении RC-цепи к замкнутым выводам С и G внутренний релаксационный генератор формирует тактовые импульсы с частотой, определяемой параметрами RC-цепи. Типовое значение частоты при RCLC =50 кОм и CCLC =47 пФ составляет 300 кГц.

Микросхемы ОМЭВМ и УМЭВМ выполнены по низкопороговой p-МОП технологии на динамической логике с использованием обедненных транзисторов в качестве нагрузок. ОМЭВМ выпускается в 40-выводном пластмассовом ДИП корпусе (рис. 4), УМЭВМ — в 48-выводном металлокерамическом ДИП корпусе (рис. 5). Основные электрические параметры и режимы эксплуатации приведены ниже.

Пример включения однокристальной микроЭВМ

На рис. 6,а приведена схема включения однокристальной микроЭВМ для реализации, простого секундомера. При нажатии на кнопку пуска начинается счет времени с отображением на 4-разрядном индикаторе десятых долей секунды, секунд, десятков секунд и минут. При нажатии на кнопки Стоп или Сброс происходит остановка счета времени или сброс секундомера соответственно. Для отсчета времени на вход D8 микроЭВМ подаются импульсы с микросхемы кварцевого генератора частотой 50 Гц. Разряды R-порта R0—R3 используются для сканирования клавиатуры и индикатора, причем высокий уровень сигнала на R-выходах соответствует разрешению свечения соответствующего разряда индикатора. Предполагается, что выходная ПЛМ закодирована для преобразования содержимого Q-регистра в коды семисегментного индикатора так, что нулевому значению Q-регистра соответствует ноль на индикаторе, единице соответствует единица на индикаторе, и так до девяти. Программа микроЭВМ, реализующая секундомер, приведена на рис. 7. В программе используются ячейки У=0...5 нулевой страницы ОЗУ данных. Назначение ячеек ОЗУ приведено на рис. 6,6.

- Скачать полный вариант статьи (со схемами, таблицами)...

УДК 621.3.049.77:681.3.06

В. Н. Златопольский, И. Е. Лобов, А. И. Стоянов, И. А. Шадрин

1984 год

Комментариев нет.